# Analysis of Quantization Noise and Power Estimation of **Continuous-Time Delta Sigma Analog-to-Digital Converter Using Test Enable Feature For 4G Radios**

Anil Kumar Sahu\*1, Vivek Kumar Chandra<sup>2</sup>, G R Sinha<sup>3</sup> <sup>1</sup> SSGI (FET), SSTC Bhilai, India <sup>2</sup> C.S.I.T Durg, India <sup>3</sup> CMR Technical Campus Hyderabad, India

# **Article Info**

TSG

# ABSTRACT

This paper presents a novel approach for completely test enable feature and Article history: low-voltage delta- sigma analog-to-digital (A/D) converters for cutting edge Received Jun 16, 2018 wireless applications. Oversampling feature of ADCs and DACs is enough to Revised Jul 10, 2018 meet the requirement related to in-band and adjacent channel leakage ratio Accepted Jul 22, 2018 (ACLR) execution of 3G/4G portable radio. The quantization noise which is not filtered in ADC is addressed. We have achieved work power-optimization and test enable feature of oversampling ADC is uses in design and simulation Keywords: so that the problem of quantization error in continues time sigma delta ADC is 4G Radio of Wireless Receiver solved. This paper suggests support to designer for selecting appropriate CORDIC topologies with various channel arrangements, number of bits and oversampling issues. A test enable feature of CT A/D is presented introducing CT DSM the test signal generation (TSG) and the COrdinate Rotation Digital Computer (CORDIC) for evaluating the performance of ADC. This helps in addressing the challenge of 4G and upcoming 5G wireless radio. System level plan of a delta-sigma modulator ADC for 4G radios is studied.

Copyright © 2018 Institute of Advanced Engineering and Science. All rights reserved.

### Corresponding Author:

Anil Kumar Sahu, Departement of Electronics and Telecommunication, SSGI (FET), SSTC Bhilai, (C.G), India. Email: anilsahu82@gmail.com

#### **INTRODUCTION** 1

Radio recurrence (RF) and mixed-signal topologies are fundamental components in future remote applications such as wireless 4G radios [1]. This type of innovation could enable the remote interchanges frameworks to relocate and help multiband and multi-standard radios, RF front-end/back-end, and advanced baseband systems. The drivers for mobile wireless communications are standards and protocols, frequency bands, power consumption, size, and cost [2].

This paper addresses the different issues in the design of future software radios 4G and 5G with emphasis on optimized power and test enable feature of oversampling analog- to-digital converters (ADCs) [3]. We have tried to review the challenges imposed on the wireless receiver design by the low-power specifications and small size in mobile terminals. The sigma-delta modulator structures that can conceivably be utilized for executing ADCs for portable remote radios are displayed in the point of view of a CMOS usage [4].

Generally, in modern luxury car, we have a cellular phone, fax, GPS receiver, television or even an internet browser in addition to radio. All these portable wireless communication systems use receivers to get the information signals from the world. The signals are received by an antenna, and the desired signal band, for example a GSM channel, is selected from the total received spectrum [5]. This frequency band undergoes analog filtering, amplification, frequency modulation and analog-to-digital conversion. Further signal

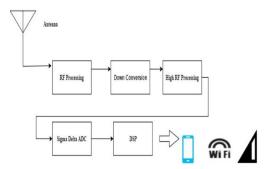

82 processing is done in the digital domain by a digital signal processor. Figure 1 shows Generic block diagram of wireless receiver which consists of an antenna, an RF/IF (Intermediate frequency) front-end, an ADC, and a digital signal processor (DSP) [6].

Figure 1. Generic Block diagram of Wireless Receiver

The ADC is used to digitize an RF, IF, or baseband signal depending on the receiver design. The location of the ADC in a receiver chain is very important that affects the overall performance, complexity, power dissipation, size, and cost [7]. The filtering and frequency translation are performed in digital domain, which reduces the complexity of the receiver and increases the flexibility. A flexible receiver consists of a digitally controlled analog front-end software-defined radio and a programmable digital back-end. The digital back-end forms the signals and feeds back control signals that reconfigures between different standards or dynamically within the same standard, the building blocks in the front-end. These blocks switch to a different set of performance values a different filter order or cut-off frequency for a filter, or a different gain and bandwidth for a low-noise amplifier, or a different gain for a variable gain amplifier, or different dynamic range and bandwidth for an ADC, etc [8]. Important tenors in the receiver design for wireless portable applications are: smaller product sizes, moderate products and longer stand-by times.

Products can be made smaller and cheaper by increasing the level of integration. Wireless communication has revolutionized everyone's lives by enabling a high speed connection directly to the people/information customers needs [12]. Wireless technologies such as 3G (third generation) and other such technologies coexist and work synergistically to meet customer needs. This requires different wireless systems that further needs multimode, multiband, and multi-standard mobile terminals. Sharing and/or switching building blocks is important requirement to extend the battery life and/or to reduce cost [9, 10]. Flexibility and adaptability are the key features in a multimode, multiband, and multi-standard wireless radio [11].

# 2. RESEARCH METHOD

# 2.1 System Level Modeling and Analysis of CT DSM Architecture as (DUT) for 4G Radio Application

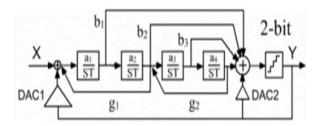

Versatile sigma delta ADC configuration is shown in Figure 2, which consist of forward path coefficient b1, b2, b3 and integrator coefficient a1, a2, a3, a4 along with two digital to analog converter (DAC) DAC1 and DAC 2 and 2 bit quantizer for multi-mode structure in 5MHz, 7MHz and 10MHz channel information exchange limits. It is a reconfigurable and programmable ADCs which covers a perfect world an information exchange limit run to upgrade power and range for a specific application, by using the same ADC structures, re-use and plan strategies. Continuous time sigma-delta (CT  $\Sigma\Delta$ ) ADCs are used as a piece of remote correspondences, where a high information transmission at low power uses is required. Despite the fact that CT  $\Sigma\Delta$  ADC offers the probability to change over high transmission limit data with a ridiculous low power usage. Table 1 gives the details about different modes of CT sigma delta ADC. In this table for wireless local area network (WLAN) in this mode feedback path (g1) and (g2) are connected and represented as dark straight line and similarly in Universal Mobile Telecommunications Service (UMTS)/Digital Video Broadcasting (DVB) (g1) feedback path trace is dashed line and (g2) feedback path trace line is dark straight line. Another mode of GSM (g1) feedback path trace and (g2) feedback path trace line is dashed straight line means unconnected. TABLE 2 shows delta sigma modulator performance and specification in 4 -G radios. In this table different parameter of CT ADCs such as Oversampling Ratio (OSR), Bandwidth (BW), Signal-To-Noise Ratio (SNR), modulation type and dynamic rang with variation of various mode of wireless along with CMOS technology is discussed.

Figure 2. System Level Model of CT DSM Architecture for 4G Radio Application

| Tabl     | e 1. Different Modes of CT Sigma Del | ta ADC                   |

|----------|--------------------------------------|--------------------------|

| MODE     | (g1) Feedback path Trace             | (g2) Feedback path Trace |

| WLAN     |                                      |                          |

| UMTS/DVB |                                      |                          |

| GSM      |                                      |                          |

Table 2. Delta Sigma Modulator Performance and Specification in 4 -G Radios

Participation of the second s

| MODE        | OSR      | BW(MHz)     | SNR (dB)  | Estimated power<br>and CMOS<br>Technology | Modulation and dynamic Rang |

|-------------|----------|-------------|-----------|-------------------------------------------|-----------------------------|

| WLAN        | 16       | 20          | 76        | 20 mW<br>(130nm)                          | BPSK/64 QAM                 |

| DVB         | 25       | 4           | 54.6-56.5 | 19 mW (180nm)                             | BPSK/64 QAM                 |

| UMTS<br>GSM | 12<br>65 | 1.92<br>0.2 | 65<br>82  | 3.5 mW (130nm)<br>1.42mW (180nm)          | BPSK/64 QAM<br>BPSK/64 QAM  |

# 2.2 GUI of Noise Calculation CT Sigma Delta ADC Used for 4G Radio

There are different types of noise signals in the circuit affecting power and the errors are addressed by the system or circuit level techniques. This reduces the noise less than 25 percent of original present. When we calculate thermal noise and the clock jitter noise, it is around 75 percent of the total noise. GUI is designed for the noise calculation of the modulator. The delay is reduced or compensated by using a fast path around the quantizer which is used in the modulator. Using fully differential architecture is used; the mismatch in the rise and fall edge of the DAC output can be reduced. Figure 3 shows the results that are obtained after executing using MATLAB. For different values of all the parameters, different values of bandwidth and power are obtained as Lc , Nc and OSR.

| т        | BW     | Rt     |              |     |       |                                     |

|----------|--------|--------|--------------|-----|-------|-------------------------------------|

| 310      | 18     | 201e9  |              |     | IBNth | 0.1362                              |

| Vfs      | Lambda | в      |              |     |       |                                     |

| 20       | 4      | 8      |              |     | NF    | 0.0002034                           |

| Sn0      | F0     | fs     | Ps           | Q   |       |                                     |

| 0.251e-3 | 10     | 25     | 14           | 40  | Sfn   | 1.1591e-09                          |

| Aled     | Lc     | Nc     |              |     |       |                                     |

| 0.95     | 3      | 4      |              |     | Ac    | -0.28331                            |

| ath      |        |        |              |     |       |                                     |

| 0.45     |        | R      | 64336133.32  | OSR |       | 0.0027628<br>0.0031435<br>0.002887  |

| st       | Y      |        |              | 8   | 16Nq  | 0.0034109<br>0.0042786              |

| 0.23     | 4      | BNLNRZ | 1.371168e+16 |     |       | 0.0035487<br>0.0035487<br>0.0032758 |

Figure 3. Noise Calculation for CT Sigma Delta ADC for 4G Radio

#### 2.3 Power Consumption of CT Sigma Delta ADC used for 4G Radio

Figure 4 shows the power consumption of CT sigma delta ADC for 4G Radio. For the calculation of power consumption the different parameters are there on which the overall power consumption depends is represent in GUI block. The analog supply voltage plays a vital role in it for calculation of power in CT sigma delta ADC.

Figure 4. Power Consumption CT Sigma Delta ADC for 4G Radio

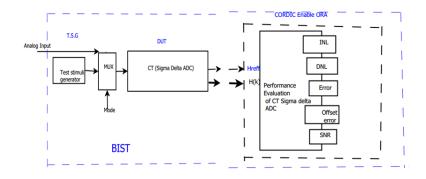

#### **2.4** $\Sigma$ - $\Delta$ Modulator ADC for Test Enable Feature for Wireless

A test enable feature of CT A/D is proposed introducing the test signal generation (TSG) and CORDIC for evaluating the performance of ADC to address the challenge of 4G and upcoming 5G wireless radio. System level plan of a delta-sigma modulator ADC for 4G radios is presented. Figure 5 shows block diagram of proposed  $\Sigma$ - $\Delta$  modulator ADC with test enable capability.

Figure 5. Block Diagram of Proposed  $\sum \Delta$  Modulator ADC with Test Enable Capability

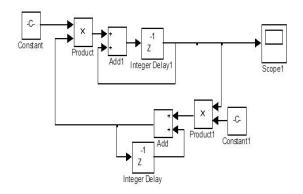

# 2.5 Test Stimulus generation and power estimation of TSG

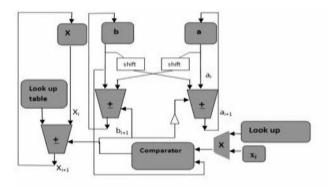

A simulink model of TSG is shown in Figure 6 which generates a sinusoidal signal which is required in subsequent stages of ADC as a test signal in ADC. Ramp signal is also required to test INL and DNL performance of ADC, which can be taken from test signal generated by TSG after converting in to ramp signal. Digital resolution based lossless (LDI) discrete integrator is used as TSG [2]. The resonators are obtained by cascading to integrator which, can be seen in Figure 6. The sinusoidal signal is generated while considering the variation in the coefficient a12 and a21 and the value of x1 and x2 fixed as  $a21=2^{-6}$ ;  $a12=2.667\times10^{-4}$ ; x1(0) = 0; x2(0) = 0.0327159 and fos= 3.063MHz.

Power consumption of TSG is written as:

$$PTSG = 2 P_{INT\_delay} + 2 P_{Multiplier} + 2 P_{Adder}$$

(1)

Where  $P_{INT\_delay}$ =power of integer delay;  $P_{Multiplier}$ = power of Multiplier unit and  $P_{Adder}$ =power of adder unit.

Figure 6. System Level Modeling of Test Stimulus Generator

#### 2.6 Modeling and Analysis of Output Response Analyzer Using CORDIC Approach

Figure 7 shows block diagram of basic CORDIC technique ORA subsystem of test enable feature used to evaluate test parameter such as Integral Non-Linearity (INL) and Diffentail Non-Linearity (DNL) etc. There are several techniques for implementing ORA and based on complexity and bit resolution CORDIC used in the present work. CORDIC technique provides iterative formulation used to evaluate some elementary function, for example logarithmic, trigonometric and division. Reference histogram is obtained using CORDIC technique which consists of major components as a MUX, Embedded CORDIC calculator and resistor. Input offset error is calculated and final value of sine wave histogram is evaluated [11].

Figure 7. Block Diagram of Basic CORDIC Technique

Another component of CORDIC to calculate static parameter of sigma delta ADC such as DNL, INL, offset error and gain error. The dynamic parameters like Signal to Noise Ratio (SNR) are also calculated using this circuit. The values of DNL, INL, offset error and SNR affect the 4 G radio performance in wireless applications so that critical evaluation of this parameters are required.

# 3. RESULTS AND ANALYSIS

Table 3 shows extracted noise parameters of CT ADCs used for 4G radio which in Band Noise (IBN) is depends on choice of bits size, availably of Bandwidth (BW), order of modulator (Lc). Table 4 shows extracted power of CT sigma delta ADC which is technology depends on power supply (Vdd) and other parameter also for 4G radio. ADC works in different modes and in each mode power optimization is needed. The GUI based noise and power estimation is modeled to meet this requirement with enabling the test feature of ADC used in wireless receiver.

Tabulated result it is notice that minimum power dissipation Pct=3.06mw is achieved when Lc=3,Nc=4,OSR=10,BW=25 MHz.

|       |    | Table 3. Extra | acted Noise Paran | neters for 4G R | adio   |         |

|-------|----|----------------|-------------------|-----------------|--------|---------|

| S.No. | Lc | Nc             | BW(MHz)           | B(bit)          | IBN_Th | IBN_NRZ |

| 1.    | 4  | 3.2            | 18                | 12.5            | 0.113  | 0.242   |

| 2.    | 4  | 1              | 36                | 13.5            | 0.240  | 0.432   |

| 3.    | 3  | 4              | 25                | 12              | 0.365  | 0.480   |

| 4.    | 3  | 1              | 60                | 10.5            | 0.149  | 0.360   |

| S. No. | Lc | Nc  | OSR  | BW(MHz) | Vdd(Volt) | Pct(Author's | Pct (In this |

|--------|----|-----|------|---------|-----------|--------------|--------------|

|        |    |     |      |         |           | work) (mw)   | paper)(mw)   |

| 1      | 4  | 3.2 | 17.8 | 18      | 1.2       | 4            | 5.56         |

| 2      | 4  | 1   | 50   | 36      | 1.2       | 14.8         | 9.45         |

| 3      | 3  | 4   | 10   | 25      | 1.2       | 6.3          | 5.32         |

| 4      | 3  | 1   | 50   | 60      | 1.4       | 18.5         | 14.79        |

| 5      | 3  | 4   | 10   | 25      | 1.2       | 5.4          | 3.06         |

#### 4. CONCLUSION

This paper discusses power productivity of various delta sigma modulator topologies used in wireless application. Power and noise estimation techniques are designed and simulated to exact the power utilization of the delta sigma modulator. The test enable features are modeled and simulated in MATLAB simulink environment for CT sigma delta ADC used in 4G radios. In this work quantization noise and other parameter are reduced significantly that were not addressed in similar research works.

#### ACKNOWLEDGEMENTS

The authors would like to thank the SSTC research center for providindg plateform to utilizing resources and Supervisior for their useful for and suggestions.

#### REFERENCES

- [1] Ke., Y, Craninckx J., Gielen G., "Design strategy for Continous-Time Delta-Sigma based on power consideration for 4G radios" *International Symposium on Signals, Circuits and Systems, Iasi*, pp.1-4, 2007.doi: 10.1109/ISSCS.2007.4292642

- [2] Morris A.S., Steel V., "Integrated tunable systems for scalable 4G radios". *IEEE MTT-S International Microwave Symposium Digest (MTT), Seattle, WA*. Pp.1-4, 2013.doi: 10.1109/MWSYM.2013.6697717

- [3] Ke Y., Gao P., Craninckx J., Van der Plas G., Gielen G.A., "2.8-to-8.5mW GSM/bluetooth/UMTS/DVB-H/WLAN fully reconfigurable CTΔΣ with 200kHz to 20MHz BW for 4G radios in 90nm digital CMOS". Symposium on VLSI Circuits, Honolulu, HI, pp.153-154, 2010..doi: 10.1109/VLSIC.2010.5560317

- [4] Tripathi G. C., Jaraut P. M. Rawat., Reddy L. N., "Low cost implementation of software defined radio for improved transmit quality of 4G signals". *Communication, Control and Intelligent Systems (CCIS), Mathura*, pp.108-112, 2015.doi: 10.1109/CCIntelS.2015.7437888

- [5] Y. Ke, J. Craninckx, G. Gielen, "A Design Approach for Power-Optimized Fully Reconfigurable \$Delta Sigma\$ A/D Converter for 4G Radios".*IEEE Transactions on Circuits and Systems II: Express Briefs*, Vol. 55,Issue 3,pp. 229-233,2008.doi: 10.1109/TCSII.2008.918974

- Veillette B. R., Roberts G. W., "A built-in self-test strategy for wireless communication systems". Proceedings of 1995 IEEE International Test Conference (ITC), Washington, DC, pp.930-939, 1995..doi: 10.1109/TEST.1995.529939

- [7] Ruotsalainen H., Arthaber H., Laakso T. I., Magerl, G., "Quantization Noise Reduction Techniques for Digital Pulsed RF Signal Generation Based on Quadrature Noise Shaped Encoding". *IEEE Transactions on Circuits and Systems I: Regular Papers, Vol.* 61, issue 9, pp. 2525-2536, 2014.doi: 10.1109/TCSI.2014.2332259.

- [8] Mallek, J., Mnif H., Loulou M., "Flexible sigma delta ADC for mobile WiMAX applications". 16th IEEE Mediterranean Electro technical Conference, Yasmine Hammamet, pp.502-505, 2012. doi: 10.1109/MELCON.2012.6196482

- [9] Roverato E., "13.4 All-digital RF transmitter in 28nm CMOS with jk programmable RX-band noise shaping". IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, pp.222-223, 2017.doi: 10.1109/ISSCC.2017.7870341

- [10] Gong F., Wu X., "System Level Power Optimization of Sigma-Delta Modulator". Design, Automation & Test in Europe Conference & Exhibition, Nice, pp. 1-4, 2007. doi: 10.1109/DATE.2007.364607.

- [11] Peng, C.S., Chuang, Y.S., Wen, K.A., "CORDIC-based architecture with channel state information for OFDM baseband receiver".*IEEE Transactions on Consumer Electronics*, Vol.51,issue 2, pp.403-412,2005.

- [12] M.M. Hossein, Y. Mohammad, "A hybrid CT/DT double-sampled SMASH sigma-delta modulator for broadband applications in 90 nm CMOS technology". Springer Science Business Media Analog, Integrated Circuit Signal Process, Vol. 73, pp.101–114, 2012.

# **BIBLIOGRAPHY OF AUTHORS**

| Mr. Anil Kumar Sahu is working as assistant professor in shrishankaracharya group of institutions,<br>Bhilai,Chattisgarh in India. He is currently pursuing his Ph.D. From Swami Vivekananda technical<br>university Bhilai. He has completed his M.Techin Microelectronics and VLSI Design from SGSIT,<br>INDORE in (2008) . He has selected as a Research Associate in BITS Pilani in 2009. He has 10<br>years of academic experience and has 45 international journal and 25 national Conference and<br>international conference publications. Prof Sahu's area of interest isin the field of Mixed signal<br>design ,VLSI testing, a front end VLSI Design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dr Vivek Kumar Chandra currently working as HOD of Electrical and Electronics Engineering in<br>Chhatrapati Shivji Institute of technology Durg, and having total 10 year of teaching experience.<br>He has published 45 researsch papers in variousConferences (25) and journals (10). He was also<br>awarded as Young Scientist in 5th Chhattisgarh Young Scientist Congress 2007 in Engineering<br>Science by ChhattisgarhCouncil of Science & Technology, Raipur (CG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Dr G R Sinha is Professor of Electronics and Communication Engineering in CMR Technical Campus Hyderabad. He obtained his B.E. (Electronics Engineering) and M.Tech. (Computer Technology) from National Institute of Technology, Raipur. He received Gold Medal for obtaining first position in the University. He received his Ph.D. in Electronics & Telecommunication Engineering from Chhattisgarh Swami Vivekanand Technical University, Bhilai. He has been Dean of Faculty and Executive Council Member of Chhattisgarh Swami Vivekanand Technical University, Bhilai. He is appointed as Expert Member in Center of Excellence (TISS-SVE) of Tat Institute of Social Sciences Mumbai India (A Prestigious Institute) for Two Years (2017-2019). He has published 196 research papers in various international and national journals and conferences. He is active reviewer and editorial member of more than 12 Reputed International Journals such IEEE Transactions on Image Processing, Elsevier Computer Methods and Programs in Biomedicine, Springer Journal of Neural Computing and Applications etc. He has reviewed research papers of many International Conferences including IEEE conferences. He has teaching and research experience of 19 years. He has been Re-elected as Chhattisgarh Representative of IEEE MP Sub-section Executive Council 2016. He has been selected as Distinguished Speaker in the field of Digital Image Processing by Computer Society of India (2015). He is recipient of many awards like TCS Award 2014 for Outstanding contributions in Campus Commune of TCS, Rajaram Bapu Patil ISTE National Award 2013 for Promising Teacher for Creative work done in Technical Education by ISTE New Delhi, Emerging Chhattisgarh Award 2005 and awarded Deshbandhu Merit Scholarship for 05 years. He has been selected as Distinguished IEEE Lecturer in IEEE India council for Bombay section. He has been elevated to Senior Member of Govt. of India. He is regular Referee of Project Grants under DST-EMR scheme of Govt. of India. He is regular Referes of Project Grants |