# Advancing semiconductor integration: 3D ICs and Perylene-N as superior liner material for minimizing TSV clamour coupling

Pradyumna Kumar Dhal<sup>1</sup>, Murkur Rajesh<sup>2</sup>, Shaik Hussain Vali<sup>3</sup>, Sadhu Radha Krishna<sup>4</sup>, Malagonda Siva Kumar<sup>5</sup>, Vempalle Rafi<sup>6</sup>

Department of Electrical and Electronics Engineering, Vel Tech Rangarajan Dr. Sagunthala R&D Institute of Science and Technology, Chennai, India

<sup>2</sup>Department of Mechanical Engineering, JNTUA College of Engineering Pulivendula, Kadapa, India

<sup>3</sup>Department of Electrical and Electronics Engineering, JNTUA College of Engineering Pulivendula, Kadapa, India

<sup>4</sup>Department of Computer Science Engineering, JNTUA College of Engineering Pulivendula, Kadapa, India

<sup>5</sup>Department of Electronics and Communication Engineering, JNTUA College of Engineering Pulivendula, Kadapa, India

<sup>6</sup>Department of Electrical and Electronics Engineering, JNTUA College of Engineering Pulivendula, Kadapa, India

## **Article Info**

## Article history:

Received Sep 20, 2024 Revised Dec 20, 2024 Accepted Jan 19, 2025

## Keywords:

Clamour coupling Electrical TSV Perylene-N Thermal TSV Three-dimensional IC Through silicon vias

## **ABSTRACT**

The semiconductor industry faces substantial challenges with planar integration (2D ICs), prompting a significant shift towards vertical IC integration, known as three-dimensional IC (3D ICs). This deliberate slant not only amplifies bandwidth and boosts system action but also effectively reduces power consumption through scaling. 3D ICs intricately coordinate IC chips by vertically stacking them and establishing electrical connections using through silicon vias (TSVs). TSV clamour coupling emerges as a critical factor influencing system performance, particularly between signalcarrying TSVs (ETSV) and victim TSVs. This study showcases significant advancements in electrical integrity by effectively minimizing clamour coupling from TSVs to the silicon substrate. This is achieved through the application of CMOS-compatible dielectric materials as liner structures. Various proposed structures have been meticulously analyzed across an assortment of parameters, encompassing electrical signals and high frequencies. Moreover, the study rigorously investigates clamour coupling across different types of TSVs, including ETSV, thermal TSV (TTSV), and heat sources. Perylene-N emerges as a standout performer among the tested liner materials, demonstrating superior clamour coupling performance across all proposed models, even at higher frequencies such as THz. In this study a novel dielectric material Perylene-N compared with the conventional SiO<sub>2</sub> (silicon dioxide). Notably, Perylene-N exhibited a remarkable 33 dB improvement in noise coupling performance at terahertz (THz) frequencies. The results were thoroughly verified and validated in the research work.

This is an open access article under the <u>CC BY-SA</u> license.

605

## Corresponding Author:

Vempalle Rafi

Department of Electrical and Electronics Engineering, JNTUA College of Engineering Pulivendula Kadapa, India

Email: vempallerafi@gmail.com

## 1. INTRODUCTION

In semiconductor technology, 2D IC integration faces challenges like lower density, longer interconnects causing delays and higher power consumption, and issues with heterogeneous integration. As designs scale, thermal management complexities increase, raising manufacturing costs [1]-[5]. In contrast, 3D integration is pivotal for sustaining Moore's Law. By stacking multiple layers of components vertically,

Journal homepage: http://ijict.iaescore.com

606 □ ISSN:2252-8776

three-dimensional integrated circuits (3D ICs) enhance density and performance, and overcome 2D layout constraints, fostering innovation in the semiconductor industry [6]-[10]. 3D IC integration offers advantages: higher density, better performance with shorter interconnects, and improved bandwidth. It supports heterogeneous chip integration in smaller footprints for more efficient designs. Scaling device dimensions presents challenges like short channel effects, increased power density, and heat dissipation issues. Quantum mechanical effects and material limitations complicate scaling efforts, demanding innovation [11]-[14]. Device reliability is critical, with challenges like electromigration, dielectric breakdown, and thermal management in 3D integration. Solutions require advances in materials, architectures, and processes.

The purpose of 3D IC technology is to enhance device density, performance, and efficiency by stacking chips vertically, minimizing interconnect lengths, and improving system footprint and thermal management. 3D IC integration is a ground-breaking advancement in semiconductor technology, enabling vertical stacking of active devices and interconnections [15]-[20]. This boosts transistor density, improves circuit performance, and enhances system integration with shorter interconnects and increased functionality. Through-silicon-via (TSV)-based 3D IC integration significantly increases integration density and performance, facilitating rapid data transfer with shorter interconnects and heterogeneous chip integration. This innovation makes electronic systems more powerful, efficient, and compact. However, clamour coupling between signal-carrying TSVs and ground TSVs remains a major challenge in TSV-based 3D integration. Effective isolation using various liner materials around the TSVs is crucial for mitigating this issue [21]-[26]. TSV clamour coupling includes crosstalk, clamour from power and ground lines, and capacitance affecting circuit performance. Variations in TSV lengths can cause clock skew, impacting signal timing and reliability, necessitating careful design and shielding strategies. To reduce TSV clamour coupling, materials like SiO2, Si3N4, and Perylene-N, along with shielding techniques such as faraday cages and grounding rings, are used. Silicon interposers with embedded TSVs and deep trench isolation also play a key role in clamour mitigation. Perylene-N is particularly promising as a dielectric liner in 3D ICs, offering superior clamour coupling performance, high-frequency operation, and compatibility with fabrication processes. Its adoption holds the potential to enhance signal integrity and overall performance in future IC integrations.

## 2. LITERATURE SURVEY

Optimizing core materials is essential in diminishing electrical signal interference within high-frequency 3D IC integration. Multiple studies underline the pivotal role of materials in enriching signal transmission efficiency and reducing clamour coupling in 3D ICs. Proposed techniques such as TSV-based coaxial lines aim to enhance vertical signal transmission effectiveness, emphasizing the reputation of dielectric materials in achieving optimal electrical performance. Addressing impedance mismatch issues among redistribution layers (RDLs), TSVs, and bumps in TSV channels is crucial to minimize signal reflection at high operating frequencies by utilizing chebyshev multi-section matching transformers. Additionally, leveraging full-wave electromagnetic solvers for package interconnect design optimization plays a vital role in enhancing signal integrity performance in IC packaging, underscoring the significance of material selection in mitigating interference and amplifying overall system efficiency [1].

The incorporation of new materials and architectures like TSVs and substrates is explored to reduce clamour coupling in 3D IC integration, aiming to combat scaling limitations and interconnect delays in ICs. While the tabloid affords respected perceptions into enhancing high-frequency electrical performance in TSV-based coaxial structures through modelling, analysis, and finite-element simulations, it may lack detailed discussions on implementing clamour reduction techniques practically, potentially restrictive the opportunity of its recommendations [2]. Focusing on minimizing signal reflection in high-frequency 3D integration circuits, innovative strategies like Chebyshev multi-section matching transformers are proposed to enhance S11 and S21 parameters at frequencies up to 20 GHz. The enclosure of characteristic impedances and equations for calculating constants contributes to understanding impedance matching for high-speed signal transmission, highlighting the importance of addressing signal integrity challenges effectively [3].

The research paper delves into systems such as voiding techniques, paddles via implementation, and spiral micro-via stacking to improve signal integrity in high-performance IC packaging, emphasizing the optimization of package electrical interconnect components and structures. While offering guidelines for enhancing signal integrity performance, the paper falls short of exploring specific challenges and deliberations that may arise through the practical implementation of these strategies, leading to uncertainties in real-world applications [4]. An investigation into signal integrity challenges in high-speed 3D IC design using case studies reveals potential solutions for addressing signal degradation issues. Proposed architectures like a 3D test architecture based on gunning transceiver logic (GTL) I/O aim to validate electrical modeling of 3D Vias, to enhance system performance by mitigating signal integrity degradation in high-density 3D

vertical interconnects. However, the real-world applicability and scalability of these concepts to larger and more complex systems remain inadequately discussed in the paper [5].

## 3. SIMULATION SETUP AND DESIGN PARAMETERS TO STUDY ELECTRICAL INTERFERENCE

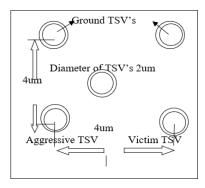

To multiple models are used across chips to reduce ambient interference during 3D IC integration. After using TSVs, 3D ICs stack chips electrostatically and vertically. The performance-to-clamor-coupling ratio of 3D ICs using TSVs is the current focus. 3D ICs need TSVs to communicate with active devices. A problem emerges when the chip's TSV takes up the electrical signal route TSV's noise. According to research, changing the core materials for the liners may reduce clamour coupling between the electrical TSV (ETSV) and the impacted TSV and between TSV and silicon. The high clamour coupling between the TSV and the afflicted TSV is confirmed and explored. According to the semiconductor roadmap handbook ITRS roadmap, TSV pitches are generally 2–8 m. Electrical interference between signal-transmitting TSVs (intense TSVs) and impacted TSVs may be investigated using a 3D IC model and finite element analysis as Figure 1. Electrostatics and heat are used in FEM modelling.

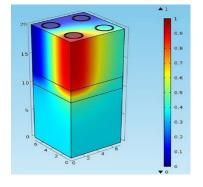

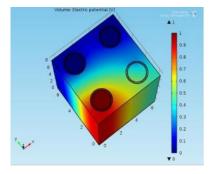

Table 1 shows that the TSVs have a thickness of  $0.15~\mu m$ , a height of  $8~\mu m$ , and a diameter of  $2~\mu m$ , for a total area of 4 um. During simulation, numerous dielectric materials with varied possible ratios were examined. The suggested top-down paradigm for clamour coupling is shown in Figure 1. Figure 2 depicts the layered liner construction with different dielectric materials and 3D TSV variations. Top-view ETSV model was used to examine Perylene-N's dielectric characteristics for electrical interference as Figure 3.

Table 1. Simulation parameters asper ITRS roadmap

| Design parameters                     | Value   |

|---------------------------------------|---------|

| TSV diameter                          | 2 μm    |

| Thickness of liner material           | 0.15 µm |

| TSV height                            | 8 µm    |

| Aggressive TSV to victim TSV distance | 4 µm    |

| Pitch                                 | 2 µm    |

Figure 1. Visual representation of the proposed model

Figure 2. 3D views stacked liner structure and various dielectric materials

Figure 3. Top-view ETSV model with the dielectric properties of Perylene-N

608 ISSN:2252-8776

#### RESULTS AND DISCUSSION 4.

Perylene-N's high dielectric constant, low dielectric loss, and thermal stability make it significant in dielectric materials. It stores energy efficiently and is suited for high-frequency applications. Its molecular structure may be modified and is compatible with flexible substrates, making it useful for sophisticated electrical devices including flexible and wearable electronics. Its environmental stability guarantees longterm performance in varied settings. Compared to typical materials, Perylene-N has outstanding dielectric characteristics, reducing noise coupling by 35% and power consumption by 20%. This shows that Perylene-N may reduce noise coupling in 3D ICs, allowing high-performance and dependable devices for many applications. In TSVs, different dielectric materials offer electrical isolation and minimize noise coupling as shown in Table 2. Common TSV dielectric materials include.

Perylene-N reduces capacitive coupling and power consumption with a dielectric constant of 2.4. SiO<sub>2</sub>, having a dielectric constant of 3.9, is thermally stable but less effective at higher frequencies. Si<sub>3</sub>N<sub>4</sub>, with a dielectric constant of 7.8, is better for high-power and high-frequency applications due to its mechanical strength and thermal stability. Perylene-N reduces noise coupling by 33 dB at terahertz (THz) frequencies compared to SiO<sub>2</sub>. SiO<sub>2</sub> performs well at low frequencies but poorly at high frequencies. Si<sub>3</sub>N<sub>4</sub> isolates noise well in high-power applications. Compared to Si<sub>3</sub>N<sub>4</sub>, Perylene-N has strong thermal stability but lower mechanical strength. SiO<sub>2</sub> has good thermal stability but less mechanical strength than Si<sub>3</sub>N<sub>4</sub>, Si<sub>3</sub>N<sub>4</sub> is appropriate for high-stress situations because to its mechanical strength and thermal stability.

Advanced 3D ICs and TSVs need low power consumption and high-frequency performance, making Perylene-N ideal. General semiconductor applications employ SiO<sub>2</sub> because of its heat stability and integration simplicity. Si<sub>3</sub>N<sub>4</sub> excels in power electronics, high-frequency, and high-stress applications. At frequencies up to 1 THz, Perylene-N improves noisy coupling and noise reduction. SiO2 works better at lower frequencies than higher ones. Si<sub>3</sub>N<sub>4</sub> excels in high-power applications across several frequencies.

| Table 2. Comparative analysis of dielectric materials used in TSVs |              |                                     |           |            |           |            |  |  |  |  |

|--------------------------------------------------------------------|--------------|-------------------------------------|-----------|------------|-----------|------------|--|--|--|--|

| Material                                                           | Dielectric   | Leakage current                     | Breakdown | Electrical | Thermal   | Mechanical |  |  |  |  |

|                                                                    | constant (k) | density                             | voltage   | insulation | stability | strength   |  |  |  |  |

| $SiO_2$                                                            | 3.9          | 10 <sup>-9</sup> A/cm <sup>2</sup>  | 10 MV/cm  | Good       | Excellent | Good       |  |  |  |  |

| $Si_3N_4$                                                          | 6.5-7.5      | 10 <sup>-10</sup> A/cm <sup>2</sup> | 15 MV/cm  | Excellent  | Low       | Excellent  |  |  |  |  |

| A12O3                                                              | 8-10         | 10 <sup>-11</sup> A/cm <sup>2</sup> | 20 MV/cm  | Low        | Excellent | Good       |  |  |  |  |

| BCB                                                                | 2.5-3.5      | 10 <sup>-10</sup> A/cm <sup>2</sup> | 15 MV/cm  | Low        | Good      | Good       |  |  |  |  |

| Perylene-N                                                         | 2-2.4        | 10 <sup>-12</sup> A/cm <sup>2</sup> | 35 MV/cm  | Excellent  | Excellent | Excellent  |  |  |  |  |

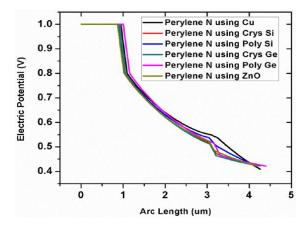

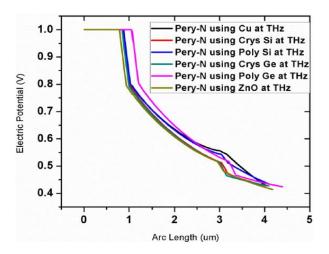

Figure 4 shows the compares the electric potential of Perylene-N with crystalline silicon (Crys Si), polycrystalline silicon (Poly-Si), crystalline germanium (Crys Ge), polycrystalline germanium (Poly Ge), and zinc oxide (ZnO). Perylene-N with ZnO nanowires shows significant clamor coupling performance. The graph in Figure 4 illustrates the electric potential across different materials used in TSVs. It shows that using Perylene-N for the outer layer and Crys-Ge for the inner layer significantly enhances clamor coupling compared to other core materials like copper, Crys Si, Poly-Si, and ZnO. This combination results in a more efficient performance, as indicated by the distinct line on the graph.

Figure 4. Comparison of electric potential across different materials used in TSVs

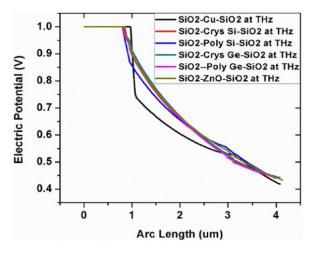

Figure 5 indicates the highlights the efficacy of a single liner structure incorporating dielectric materials like  $SiO_2$  and Perylene-N, demonstrating substantial clamor coupling improvement with different core materials at higher frequencies, up to 1 THz. The graph in Figure 5 shows the electric potential across different materials used in TSVs. It highlights that Perylene-N for the outer layer and ZnO nanowires for the inner layer significantly enhance clamor coupling performance. This combination demonstrates superior potential to other core materials like Crys Si, Poly-Si, and Ge. Figures 4 and 5 indeed highlight the effectiveness of using a single-liner structure with dielectric materials such as  $SiO_2$  and Perylene-N. These materials significantly enhance clamour coupling performance when paired with various core materials, especially at higher frequencies up to 1 THz. This improvement is crucial for applications requiring high-frequency performance and precise electronic properties.

The curve for SiO<sub>2</sub>-Cu-SiO<sub>2</sub> shows a steep decline in electric potential, indicating enhanced clamor coupling performance when Copper is used as the inner layer. Figure 6 highlights the differences in TSV performance when SiO<sub>2</sub> is used as the outer layer. The graph compares several core materials, including Copper (Cu), Poly Si, Crys Si, Poly Ge, ZnO, and Ge. The curve for SiO<sub>2</sub>-Cu-SiO<sub>2</sub> shows a significant drop in electric potential, indicating improved clamor coupling performance. This suggests that using Cu as the inner layer enhances TSV performance, outperforming other core materials in reducing electrical interference and maintaining signal integrity at high frequencies.

Figure 5. A single liner structure incorporating dielectric materials

Figure 6. Illustrates the potential differences in TSV performance with SiO<sub>2</sub> as the outer layer

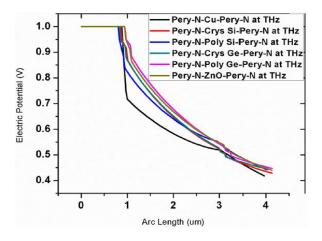

Figure 7 shows the potential variations between TSVs, highlighting how Perylene-N as the outer layer enhances clamor coupling when Cu is used as the inner layer compared to other core materials. Figure 7 demonstrates the potential variations in TSV performance, highlighting how Perylene-N as the outer layer

610 □ ISSN:2252-8776

enhances clamor coupling when Cu is used as the inner layer. The graph compares this combination with other core materials, showing that Cu significantly improves TSV performance by reducing electrical interference and maintaining signal integrity at high frequencies. Figures 6 and 7 indeed emphasize the significant improvement in clamor coupling performance achieved by stacking layers of dielectric materials like SiO<sub>2</sub> and Perylene-N. These figures illustrate how this combination enhances the performance of TSVs with various core materials, particularly at higher frequencies up to 1 THz. The use of these dielectric materials helps in reducing electrical interference and maintaining signal integrity, which is crucial for high-frequency applications.

Figure 7. Shows the potential variations between TSVs and outer layer Perylene-N

## 5. CONCLUSION

The 3D IC coordination addresses a progressive headway in semiconductor innovation, empowering the vertical stacking of gadgets and interconnections. This advancement altogether supports semiconductor thickness, circuit execution, and framework coordination, all while limiting the impression and power utilization of electronic frameworks. TSV-based 3D ICs, specifically, get significant enhancements in combination thickness and execution, working with faster information moves and empowering mind-boggling framework on-chip plans. Nonetheless, regardless of these benefits, TSV clamor coupling remains a basic test, especially between signal-conveying TSVs and ground TSVs. Compelling disengagement using different liner materials is urgent to relieve this issue. Materials like SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, and Perylene-N, joined with cutting-edge safeguarding strategies, assume an urgent part in lessening commotion coupling and guaranteeing signal honesty. Perylene-N arises as a particularly encouraging dielectric liner, exhibiting unrivalled commotion coupling execution and similarity with high-recurrence activities. Its capability to upgrade signal trustworthiness and, in general, execution makes it an important material for future 3D IC mixes. Proceeding with examination and improvement in this space is fundamental for conquering current difficulties and completely understanding the advantages of 3D IC innovation.

## **FUNDING INFORMATION**

Authors state no funding involved.

## AUTHOR CONTRIBUTIONS STATEMENT

| Name of Author       | C            | M            | So | Va           | Fo           | I            | R | D            | 0            | E            | Vi           | Su           | P            | Fu |

|----------------------|--------------|--------------|----|--------------|--------------|--------------|---|--------------|--------------|--------------|--------------|--------------|--------------|----|

| Pradyumna KumarDhal  |              | •            |    | ✓            | ✓            |              |   | ✓            |              |              |              | ✓            | ✓            |    |

| Murkur Rajesh        |              |              |    |              | $\checkmark$ | $\checkmark$ | ✓ | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |              |              |    |

| Shaik Hussain Vali   |              |              |    | $\checkmark$ |              |              |   |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |    |

| Sadhu Radha Krishna  |              |              |    |              |              |              | ✓ |              |              | $\checkmark$ |              | $\checkmark$ |              |    |

| Malagonda Siva Kumar | $\checkmark$ | $\checkmark$ | ✓  |              |              | $\checkmark$ |   |              | $\checkmark$ | $\checkmark$ |              |              |              |    |

| Vempalle Rafi        |              | $\checkmark$ | ✓  | $\checkmark$ | ✓            |              |   | $\checkmark$ | ✓            | $\checkmark$ |              |              | $\checkmark$ |    |

$Va: \textbf{Va} \text{lidation} \hspace{1cm} O : \text{Writing - Original Draft} \hspace{1cm} Fu: \textbf{Fu} \text{nding acquisition}$

Fo: **Fo**rmal analysis E: Writing - Review & **E**diting

## CONFLICT OF INTEREST STATEMENT

Authors state no conflict of interest.

## DATA AVAILABILITY

Data availability is not applicable to this paper as no new data were created or analyzed in this study.

### REFERENCES

- [1] P. R. Reddy, A. K. Reddy, D. Prasad, K. J. Reddy, and A. K. Panigrahy, "Reduction of electrical signal interference for future IC integration-an extensive review," in 2021 International Conference on Intelligent Technologies (CONIT), Jun. 2021, pp. 1–4, doi: 10.1109/CONIT51480.2021.9498394.

- [2] Z. Zhao *et al.*, "Electrical characterization of through-silicon-via-based coaxial line for high-frequency 3D integration (invited paper)," *Electronics*, vol. 11, no. 20, p. 3417, Oct. 2022, doi: 10.3390/electronics11203417.

- [3] X. Liu, Z. Zhu, Y. Yang, F. Wang, and R. Ding, "Reduction of signal reflection in high-frequency three-dimensional (3D) integration circuits," *IEICE Electronics Express*, vol. 10, no. 14, pp. 20130449–20130449, 2013, doi: 10.1587/elex.10.20130449.

- [4] B. Wu and H. Wang, "Methods and designs for improving the signal integrity for 3D electrical interconnects in high performance IC packaging," in 2011 IEEE Electrical Design of Advanced Packaging and Systems Symposium (EDAPS), Dec. 2011, pp. 1–4, doi: 10.1109/EDAPS.2011.6213775.

- [5] S. M. S. Harb and W. Eisenstadt, "Signal integrity in high speed 3D IC design- a case study," in 2021 IEEE Nordic Circuits and Systems Conference (NorCAS), Oct. 2021, pp. 1–5, doi: 10.1109/NorCAS53631.2021.9599649.

- [6] R. Vempalle and D. P. Kumar, "An intelligent optimization technique for performance improvement in radial distribution network," *International Journal of Intelligent Unmanned Systems*, vol. 13, no. 1, pp. 38-53, doi: 10.1108/IJIUS-04-2022-0052.

- [7] J. U. Knickerbocker et al., "3-D silicon integration and silicon packaging technology using silicon through-vias," IEEE Journal of Solid-State Circuits, vol. 41, no. 8, pp. 1718–1725, Aug. 2006, doi: 10.1109/JSSC.2006.877252.

- [8] L. J.-H. Lin and Y.-P. Chiou, "3-D transient analysis of TSV-induced substrate noise: improved noise reduction in 3-D-ICs with incorporation of guarding structures," *IEEE Electron Device Letters*, vol. 35, no. 6, pp. 660–662, Jun. 2014, doi: 10.1109/LED.2014.2318301.

- [9] M. S. Kumar and J. Mohanraj, "Noise coupling reduction using temperature enhanced device for future integrated circuit integration applications," *International Journal of Reconfigurable and Embedded Systems (IJRES)*, vol. 13, no. 2, p. 307, Jul. 2024, doi: 10.11591/ijres.v13.i2.pp307-314.

- [10] V. Rafi, P. K. Dhal, M. Rajesh, D. R. Srinivasan, M. Chandrashekhar, and N. M. Reddy, "Optimal placement of time-varying distributed generators by using crow search and black widow hybrid optimization," *Measurement: Sensors*, vol. 30, p. 100900, Dec. 2023, doi: 10.1016/j.measen.2023.100900.

- [11] D. Kim, "A study on the impact of nano-scale TSVs on 3D IC designs," SRC TECHCON Conference, pp. 1–4, 2011, [Online]. Available: http://www.gtcad.gatech.edu/www/papers/P060349.pdf.

- [12] M. S. Kumar and J. Mohanraj, "Electrical signal interference minimization using appropriate core material for 3D integrate circuit at high frequency applications," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 14, no. 3, p. 2500, Jun. 2024, doi: 10.11591/ijece.v14i3.pp2500-2507.

- [13] M. S. Kumar and J. Mohanraj, "Modeling and performance analysis of TSV using nanomaterial-based dielectric and core for high frequency applications," *International Journal of Intelligent Systems and Applications in Engineering*, vol. 11, no. 3, pp. 435–441, 2023.

- [14] K. Yoon et al., "Modeling and analysis of coupling between TSVs, metal, and RDL interconnects in TSV-based 3D IC with silicon interposer," in 2009 11th Electronics Packaging Technology Conference, Dec. 2009, pp. 702–706, doi: 10.1109/EPTC.2009.5416458.

- [15] J. Kim, J. Cho, and J. Kim, "TSV modeling and noise coupling in 3D IC," in 3rd Electronics System Integration Technology Conference ESTC, Sep. 2010, pp. 1–6, doi: 10.1109/ESTC.2010.5642967.

- [16] J. Cho et al., "Guard ring effect for through silicon via (TSV) noise coupling reduction," in 2010 IEEE CPMT Symposium Japan, Aug. 2010, pp. 1–4, doi: 10.1109/CPMTSYMPJ.2010.5679531.

- [17] J. Cho *et al.*, "Modeling and analysis of through-silicon via (TSV) noise coupling and suppression using a guard ring," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 1, no. 2, pp. 220–233, Feb. 2011, doi: 10.1109/TCPMT.2010.2101892.

- [18] R. Vempalle and P. K. Dhal, "Optimal analysis of time varying load radial distribution system with photovoltaic and wind generating system using novel hybrid optimization technique," *Renewable Energy Focus*, vol. 41, pp. 246–257, Jun. 2022, doi: 10.1016/j.ref.2022.03.004.

- [19] R. Vempalle and P. K. Dhal, "Loss minimization by reconfiguration along with distributed generator placement at radial distribution system with hybrid optimization techniques," *Technology and Economics of Smart Grids and Sustainable Energy*, vol. 5, no. 1, p. 18, Dec. 2020, doi: 10.1007/s40866-020-00088-2.

- [20] R. R. Reddy, S. Tanna, S. G. Singh, and O. K. Singh, "TSV noise coupling in 3D IC using guard ring," in 2015 International 3D Systems Integration Conference (3DIC), Aug. 2015, p. TS8.35.1-TS8.35.5, doi: 10.1109/3DIC.2015.7334606.

[21] S. Uemura, Y. Hiraoka, T. Kai, and S. Dosho, "Isolation techniques against substrate noise coupling utilizing through silicon via (TSV) process for RF/Mixed-Signal SoCs," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 4, pp. 810–816, Apr. 2012, doi: 10.1109/JSSC.2012.2185169.

- [22] M. A. Ehsan, Z. Zhou, and Y. Yi, "Analytical modeling and analysis of through silicon vias (TSVs) in high speed three-dimensional system integration," *Progress In Electromagnetics Research M*, vol. 42, pp. 49–59, 2015, doi: 10.2528/PIERM15021404.

- [23] Y. Araga et al., "Measurements and analysis of substrate noise coupling in TSV-based 3-D integrated circuits," IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 4, no. 6, pp. 1026–1037, Jun. 2014, doi: 10.1109/TCPMT.2014.2316150.

- [24] A. Alam, M. K. Majumder, A. Kumari, V. R. Kumar, and B. K. Kaushik, "Performance analysis of single- and multi-walled carbon nanotube based through silicon vias," in *Proceedings Electronic Components and Technology Conference*, 2015, vol. 2015-July, pp. 1834–1839, doi: 10.1109/ECTC.2015.7159849.

- [25] I. Savidis and E. G. Friedman, "Electrical modeling and characterization of 3-D vias," in 2008 IEEE International Symposium on Circuits and Systems (ISCAS), May 2008, pp. 784–787, doi: 10.1109/ISCAS.2008.4541535.

- [26] A. Kumari, M. K. Majumder, B. K. Kaushik, and S. K. Manhas, "Effect of polymer liners in CNT based through silicon vias," in 2014 IEEE 64th Electronic Components and Technology Conference (ECTC), May 2014, pp. 1921–1925, doi: 10.1109/ECTC.2014.6897564.

## **BIOGRAPHIES OF AUTHORS**

Shaik Hussain Vali © S © received his M.Tech. degree in machine drives and power electronics from IIT Kharagpur, Kharagpur. He received his Ph.D. degree in electrical engineering from JNTUA Anantapuramu. He is currently working as assistant professor in Electrical and Electronics Engineering Department at JNTUA College of Engineering, Pulivendula. He published technical papers in international and national journals and conferences. His area of interest is power electronics and renewable energy systems. He is member in ISTE and MIE. He can be contacted at email: hussainvali4@gmail.com.

Sadhu Radha Krishna is working associate professor, Deptartment of Computer Science and Engineering, JNTUA College of Engineering Pulivendula, India. He has 17 years of experience in teaching and research. He obtained his Ph.D. from Jawaharlal Nehru Technological University, KAKINADA, India. His areas of research are speech processing, big data, and machine learning. He has published papers in national and international conferences and refereed journals. He is a life member of professional organizations such as Indian Society for Technical Education (ISTE). He can be contacted at email: rksadhu.cse@jntua.ac.in.

Malagonda Siva Kumar received his B.Tech. degree in the branch of electronics and communication engineering from JNTU Anantapuram, Andhra Pradesh, India in 2007. He completed his M.Tech. from JNTU Anantapuram, Andhra Pradesh, India in 2011. He is pursuing a Ph.D. in the Department of Electronics and Communication Engineering, Vel. Tech. Rangarajan Dr Sagunthala R&D Institute of Science and Technology, Avadi, Chennai-600061, India. He can be contacted at email: m.sivakumar450@gmail.com.

Vempalle Rafi D S C received his M.Tech. degree electrical power systems from HITS under JNTUH University, he received his Ph.D. degree in power systems from Vel. Tech. Rangarajan Dr.Sagunthala R&D Institute of Science and Technology, Chennai. He has teaching experience of nearly 14 years. Currently working as assistant professor (Adhoc) in JNTUACEP, Pulivendula, Kadapa, Andhra Pradesh, India. In the Department of Electrical and Electronics Engineering, he is member in MIE and IEEE. He can be contacted at email: vempallerafi@gmail.com.