# A comparative study and design investigation: scalable magnitude comparators across technology nodes

Anitha Juliette Albert<sup>1</sup>, Umamaheswari Ramalingam<sup>2</sup>, Ashlin Leon A. S.<sup>1</sup>, Sinthia Panneer Selvam<sup>3</sup>, Sripriya Thiagarajan<sup>4</sup>, Arunkumar Kuppusamy<sup>5</sup>

<sup>1</sup>Department of Electronics and Communication Engineering, Loyola-ICAM College of Engineering and Technology, Chennai, India

<sup>2</sup>Department of Computer Science Engineering, Saveetha Engineering College, Chennai, India

<sup>3</sup>Department of Biomedical Engineering, Saveetha Engineering College, Chennai, India

<sup>4</sup>Department of Electronics and Communication Engineering, Jeppiaar Institute of Technology, Sunguvarchatram, India

<sup>5</sup>Department of Electronics and Communication Engineering, Saveetha Engineering College, Chennai, India

### **Article Info**

#### Article history:

Received Sep 24, 2024 Revised Jun 28, 2025 Accepted Aug 6, 2025

### Keywords:

CMOS FPGA Magnitude comparator Pipelined Power delay product Technology

### **ABSTRACT**

In recent times, the convergence of innovative design technologies such as very large-scale integration (VLSI), cadence design systems, and field-programmable gate array (FPGA) has become crucial to address the growing demand for enhanced efficiency, scalability, and reduced power consumption in electronic designs. This paper introduces a novel approach to designing non-pipelined and pipelined scalable magnitude comparators (MCs), which integrates 4-bit MCs. The frontend implementation of the MCs is achieved using quartus prime, an FPGA board. The backend implementation is done using cadence design system, evaluated across the three distinct CMOS technology nodes. The literature review highlights the influence of technology scaling on area, power consumption, and propagation delay, analyzing various comparator designs and their associated trade-offs. The results provide valuable insights into the design and optimization of MCs for future applications in image processing and nano computing.

This is an open access article under the <u>CC BY-SA</u> license.

### Corresponding Author:

Umamaheswari Ramalingam

Department of Computer Science Engineering, Saveetha Engineering College

Chennai, Tamil Nadu, India

Email: umaece82@gmail.com

# 1. INTRODUCTION

The selection of an arithmetic system plays a crucial role in shaping the design of a digital system. It influences factors such as the number of required operations, the signal activity level, and the operator strength or complexity. Design of integrated circuits (ICs) is realized architecture level [1], [2], device level, and circuit level abstractions [3], [4]. The primary function of a magnitude comparator (MC) is to compare two binary numbers, starting with the least significant bit. A 4-bit MC specifically handles the comparison of 4-bit binary values, yielding results such as greater than (A > B), less than (A < B), and equal to (A = B). The number of bits compared is influenced by factors like area, static power, and dynamic power consumption. Various technology nodes are available for implementation, each suited to different scenarios. As technology advances, the size of the components typically decreases. MC plays a crucial role in arithmetic units within microprocessors, controllers, and various digital design systems. One of its primary applications is in decoding within computer systems, as well as in control logic and error detection during data transmission [5]. It has a significant application impact in image and signal processing applications [6], [7], analog-to-digital converters [8], [9], and IoT applications [10], [11]. Various implementations of MC logic,

14 □ ISSN: 2252-8776

such as CMOS [12], transmission gate, pass transistor [13], gate-diffused input (GDI) approaches [14]-[17], and carbon nano tube FET [18] have been explored. While the GDI approach excels in minimizing propagation delay, transistor count, and power consumption, it struggles with achieving a full rail-to-rail swing. The reduced swing voltage results in slower switching, which can hinder device performance. Addressing this slow switching issue is essential to prevent a decrease in operational speed.

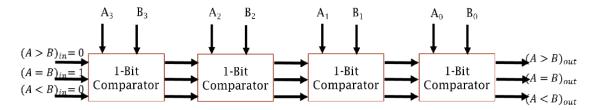

The area, along with static and dynamic power, significantly affects the number of bits that can be compared. As the number of bits increases, issues such as area constraints, power consumption, and propagation delay become more pronounced. It is important to note that leakage power increases proportionally with the device's size, which can decrease overall efficiency. Therefore, choosing the smallest possible size is generally recommended. A key advantage of this approach is that as feature size decreases, the channel length shortens. While this helps lower the threshold voltage, it can also lead to an increase in sub-threshold leakage current. The exploration of implementing MCs over technology nodes is thus significant [19]-[22]. Alternatively, in literature, comparators have been realized using quantum cell automata technology [23]-[25], XOR and OR gates [26], and majority logic [27]. Figure 1 illustrates the block diagram of a 4-bit MC, this paper's fundamental unit of consideration.

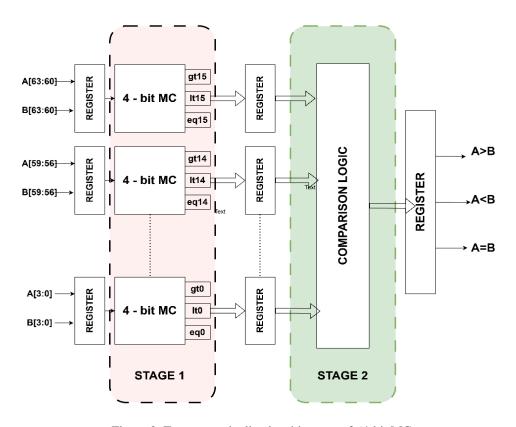

In this research paper, scalable MC's of 4, 8, 16, 32, and 64 bits are designed and implemented on a field-programmable gate array (FPGA). Additionally, at the physical design level, comparators are analyzed using 180 nm, 90 nm, and 45 nm CMOS technology. The paper presents a detailed comparison of area and power consumption results. Figure 2 depicts a 64-bit two stage pipelined MC.

Figure 1. Representation of 4-bit MC

Figure 2. Two stage pipelined architecture of 64-bit MC

It also provides an overview of the comparator design process in Quartus and its implementation on FPGA. Performance metrics such as total power consumption, switching power, leakage power, sequential logic power, combinational logic power, and total area utilization are evaluated for each CMOS technology node. The paper is structured as follows: section 2 presents the design methodology and section 3 discusses the results. The final section provides the conclusion.

#### 2. RESEARCH METHOD

The design flow for the scalable MC starts with FPGA design using Intel Quartus software. In this phase, a Verilog description and testbench are developed, followed by compilation, pin configuration mapping, and testing on the FPGA, Altera DE1-SoC board-Cyclone V- 5CSEMA5F31C6, to validate the output. Once the functionality is confirmed, the process transitions to the physical design phase. During this phase, the register-transfer level (RTL) viewer and waveform are generated using Cadence Nclaunch, providing insights into the design's behavior. The design is then synthesized using Genus, with an remote command (RC) script guiding the synthesis process. Cadence software is a suite of electronic design automation (EDA) tools widely used in the semiconductor industry. It supports the design and verification of ICs and PCBs. The software covers various design aspects, mainly including schematic capture, simulation, synthesis, layout, and verification. Cadence is particularly known for its applications in very large scale integration (VLSI) design and custom IC design, offering a comprehensive solution for the development of complex electronic systems.

In the semiconductor industry, a graphic data system (GDS) file is a binary format that is necessary for exchanging and storing IC layout information. Standardizing geometric and layer data, it makes EDA tools more well-matched with one another and promotes collaborative design. In order to create photomasks for the semiconductor manufacturing process, GDS files are essential since they specify the complex patterns needed for the fabrication process.

The paper highlights the below objectives:

- Design scalable non-pipelined and pipelined MC circuits in Quartus.

- RTL simulation for MCs.

- Generate physical layout using Cadence.

- Create GDS file for 180 nm, 90 nm, 45 nm technology.

- Comparison of power, delay and area across technology.

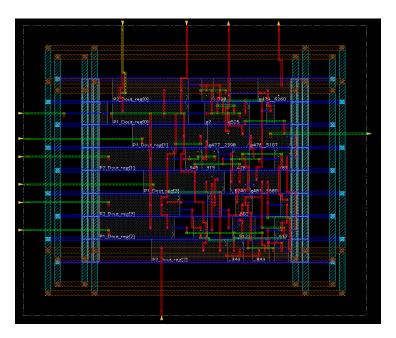

The physical design phase progresses with the use of Cadence Innovus, where key steps such as netlisting, floorplanning, power planning, standard cell placement, and routing with timing optimization are carried out. Clock tree synthesis is performed to ensure efficient and reliable distribution of the clock signal. Figure 3 illustrates the physical design of 64 bit non-pipelined comparator, synthezised at 90 nm CMOS technology.

Figure 3. Physical design of 64-Bit non-pipelined MC at 90 nm

16 ☐ ISSN: 2252-8776

After completing these processes, further optimization is carried out using engineering change order (ECO) techniques and NanoRoute. This stage is essential for improving the overall efficiency and performance of the design. Verification steps, including design rule check (DRC) and connectivity checks, are also performed to ensure the design's accuracy and integrity. As the design nears completion, design files, netlists, and the GDS file are generated. Optionally, a 3D model of the design can also be created. The final steps involve rigorous verification to ensure that the design complies with DRC and connectivity rules while meeting all specified requirements and design objectives. This systematic design flow ensures a smooth progression from conceptualization to the finalized and fully verified scalable MCs.

### 3. RESULTS AND DISCUSSION

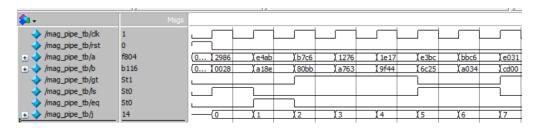

The non-pipelined and pipelined versions of the 4-bit, 8-bit, 16-bit, 32-bit and 64-bit MCs were targeted on Altera DE1-SoC board-Cyclone V- 5CSEMA5F31C6. The designs were tested for a random set of 5000 test vectors. The functional simulation result is depicted in Figure 4. The outputs gt, ls, and eq specifies the greater than, less than and equal to conditions with respect to the magnitudes of inputs a and b.

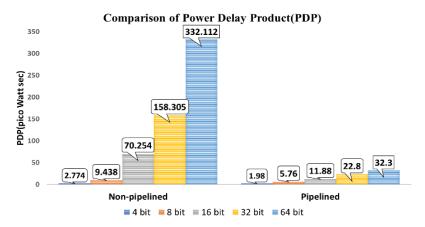

The synopsys design constraint (SDC) files were set and value change dump (VCD) files were generated to determine the power and maximum frequency of operation. Comparison of the results of power and maximum frequency of operation of the magnitude compartor for varied widths are summarized in Table 1. A comparison of the power delay product (PDP) is presented in Figure 5.

Figure 4. Simulation result of a 64-bit pipelined MC

Table 1. Power and maximum delay comparison of comparators of varied widths - Altera DE1-SoC board

| Comparator             | Power (mW) | Delay (ns) | PDP (pico Ws) |  |  |  |

|------------------------|------------|------------|---------------|--|--|--|

| 4 bit - Non Pipelined  | 1.46       | 1.9        | 2.774         |  |  |  |

| 8 bit - Non Pipelined  | 4.29       | 2.2        | 9.438         |  |  |  |

| 16 bit - Non Pipelined | 26.02      | 2.7        | 70.254        |  |  |  |

| 32 bit - Non Pipelined | 45.23      | 3.5        | 158.305       |  |  |  |

| 64 bit - Non Pipelined | 65.12      | 5.1        | 332.112       |  |  |  |

| 4 bit - Pipelined      | 1.1        | 1.8        | 1.98          |  |  |  |

| 8 bit - Pipelined      | 3.2        | 1.8        | 5.76          |  |  |  |

| 16 bit - Pipelined     | 6.6        | 1.8        | 11.88         |  |  |  |

| 32 bit - Pipelined     | 12         | 1.9        | 22.8          |  |  |  |

| 64 bit - Pipelined     | 17         | 1.9        | 32.3          |  |  |  |

Figure 5. PDP metrics of comparator designs - Altera DE1 SoC board

The power of MC's implemented on FPGA shows low power consumption by pipelined architectures when compared with the non-pipelined architectures. Pipelined architectures speed up the operation. On the whole, the results depict the reduction in PDP of the 4-bit, 8-bit, 16-bit, 32-bit, and 64-bit pipelined multipliers by 29%, 38%,83%, 85%, and 90% respectively. It is evident that as the the number of bits of comparator scales up, the pipelined architecture is preferred compared to the non-pipelined architectures. Additionally, the designs were synthesized using Cadence genus tool with the CMOS technology libraries – 180 nm, 90 nm, and 45 nm. The power, delay, area and PDP of the designs generated for the various technology nodes for the pipelined and non-pipelined architectures are summarized in Table 2. A comparison of the PDP of the comparator designs across various technology nodes is depicted in Figure 6.

Table 2. Power, delay and area comparison of comparators of varied widths across various technology

|       |            |            |           |            | noues –    | Cadence     | ,         |            |       |             |         |  |  |

|-------|------------|------------|-----------|------------|------------|-------------|-----------|------------|-------|-------------|---------|--|--|

| Bits  | Technology |            | Nor       | n-pipeline | ed         |             | Pipelined |            |       |             |         |  |  |

|       | node       | Power (mW) |           |            | Delay (ns) | Area        |           |            | •     | Delay       | Area    |  |  |

|       |            |            |           |            |            | $(\mu m^2)$ |           | Power (mW) | (ns)  | $(\mu m^2)$ |         |  |  |

|       |            | Static     | Switching | Total      |            |             | Static    | Switching  | Total |             |         |  |  |

| 4 bit | 180 nm     | 0.54       | 0.21      | 0.75       | 0.797      | 1034        | 0.42      | 0.23       | 0.65  | 0.387       | 2036    |  |  |

|       | 90 nm      | 0.15       | 0.06      | 0.21       | 0.564      | 308.8       | 0.04      | 0.14       | 0.18  | 0.321       | 421.1   |  |  |

|       | 45 nm      | 0.1        | 0.07      | 0.17       | 0.355      | 252         | 0.02      | 0.11       | 0.13  | 0.215       | 311     |  |  |

| 8 bit | 180 nm     | 0.94       | 0.3       | 1.24       | 1.424      | 1879        | 1.11      | 0.24       | 1.35  | 0.646       | 2228.6  |  |  |

|       | 90 nm      | 0.26       | 0.07      | 0.33       | 0.933      | 566         | 0.30      | 0.05       | 0.35  | 0.384       | 677.4   |  |  |

|       | 45 nm      | 0.18       | 0.09      | 0.27       | 0.501      | 421         | 0.2       | 0.04       | 0.24  | 0.388       | 511     |  |  |

| 16    | 180 nm     | 1.84       | 0.47      | 2.31       | 1.704      | 3918        | 2.09      | 0.4        | 2.49  | 0.646       | 4134.7  |  |  |

| bit   | 90 nm      | 0.48       | 0.1       | 0.58       | 1.645      | 1067        | 0.56      | 0.08       | 0.64  | 0.384       | 1251.9  |  |  |

|       | 45 nm      | 0.32       | 0.13      | 0.45       | 0.849      | 654         | 0.36      | 0.06       | 0.42  | 0.402       | 876     |  |  |

| 32    | 180 nm     | 3.36       | 0.82      | 4.18       | 1.683      | 7274        | 4.02      | 0.74       | 4.76  | 0.646       | 7920.1  |  |  |

| bit   | 90 nm      | 0.87       | 0.14      | 1.01       | 1.7        | 2165        | 1.07      | 0.14       | 1.21  | 0.384       | 2388    |  |  |

|       | 45 nm      | 0.6        | 0.19      | 0.79       | 1.586      | 1232        | 0.71      | 0.09       | 0.80  | 0.402       | 2132    |  |  |

| 64    | 180 nm     | 6.91       | 1.58      | 8.49       | 1.619      | 14968       | 7.88      | 1.42       | 9.30  | 0.646       | 15474.3 |  |  |

| bit   | 90 nm      | 1.75       | 0.29      | 2.04       | 1.711      | 4429        | 2.08      | 0.29       | 2.37  | 0.384       | 4650.3  |  |  |

|       | 45 nm      | 1.24       | 0.34      | 1.58       | 1.667      | 3954        | 1.37      | 0.17       | 1.54  | 0.375       | 4783    |  |  |

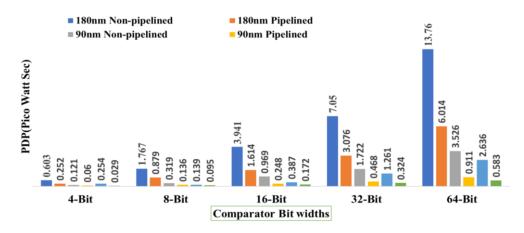

#### Power Delay Product(PDP) across various technology nodes

Figure 6. PDP metrics of comparator designs across technology nodes – 180 nm, 90 nm, 45 nm

In the case of 180 nm technology, switching power consumption is the primary contributor to overall power use, while for 45 nm technology, internal power consumption is the most significant factor. All three technologies demonstrate very low leakage power consumption. Additionally, both the 180 nm and 90 nm technologies show higher sequential logic power consumption compared to the 45 nm technology. This is primarily because sequential logic circuits typically utilize more transistors than combinational logic circuits. The PDP of all 4, 8, 16, 32, and 64 bit comparators present a 95% reduction in PDP as they transit from 180 nm to 45 nm from non-pipelined architecture to pipelined architectures.

18 □ ISSN: 2252-8776

The 45 nm process technology exhibits higher combinational logic power consumption compared to the 180 nm and 90 nm technologies. This is because combinational logic circuits generally incorporate more complex gates than sequential logic circuits. Overall, the 45 nm manufacturing technology offers the best performance-to-power ratio. One significant finding is the total area metric, which indicates the physical space occupied by each process technology's design. As process technology advances, there is a clear trend of decreasing area, evidenced by an average reduction of 75% for 4, 8, 16, 32, and 64 bit comparators for transition from 180 nm to 45 nm technology. This decrease is attributed to the use of smaller transistors, which enables greater functionality to be integrated into a more compact space. The key takeaway is that, as demonstrated by the 45 nm example, a lower process technology results in a significantly smaller area. This is a crucial advantage in modern chip design, allowing for increased functionality or higher density within the same physical constraints. Importantly, the core design integrity is maintained despite these advancements, focusing on optimization rather than a complete overhaul of the underlying principles.

### 4. CONCLUSION

This paper explores the design of a scalable MC - 4, 8, 16, 32, and 64-bit non-pipelined and pipelined utilizing Quartus Prime, FPGA technology, and the cadence design system across three technology nodes: 180 nm, 90 nm, and 45 nm. The results include 3D layouts and GDS files for each technology node, demonstrating that the 45 nm process technology has the lowest overall power usage. The power consumption analysis highlights several factors, including internal power, switching power, leakage power, sequential logic power, and combinational logic power, with the 45 nm technology showing a superior performance-to-power ratio. The area comparison reveals a significant reduction in physical size as technology nodes advance, while the instance count remains consistent, reflecting stable underlying design logic across all nodes. In summary, this study offers valuable insights into the trade-offs between power consumption, performance, and physical size in the design of a 4-bit MC across different technology nodes.

#### **FUNDING INFORMATION**

Authors state no funding involved.

# **AUTHOR CONTRIBUTIONS STATEMENT**

This journal uses the Contributor Roles Taxonomy (CRediT) to recognize individual author contributions, reduce authorship disputes, and facilitate collaboration.

| Name of Author         | C            | M            | So | Va           | Fo           | I            | R | D            | 0            | E            | Vi | Su           | P            | Fu |

|------------------------|--------------|--------------|----|--------------|--------------|--------------|---|--------------|--------------|--------------|----|--------------|--------------|----|

| Anitha Juliette Albert | ✓            | ✓            | ✓  | ✓            | ✓            | ✓            | ✓ | ✓            | ✓            | ✓            | ✓  | ✓            | ✓            |    |

| Umamaheswari           | $\checkmark$ | $\checkmark$ |    | $\checkmark$ |              | $\checkmark$ | ✓ | $\checkmark$ | $\checkmark$ | $\checkmark$ | ✓  | $\checkmark$ | $\checkmark$ |    |

| Ramalingam             |              |              |    |              |              |              |   |              |              |              |    |              |              |    |

| Ashlin Leon A. S.      |              |              | ✓  | $\checkmark$ |              |              |   | $\checkmark$ |              |              | ✓  |              |              |    |

| Sinthia Panneer        |              |              | ✓  | $\checkmark$ |              |              | ✓ |              |              | $\checkmark$ | ✓  |              |              |    |

| Selvam                 |              |              |    |              |              |              |   |              |              |              |    |              |              |    |

| Sripriya Thiagarajan   |              |              | ✓  | $\checkmark$ |              |              | ✓ |              |              | $\checkmark$ | ✓  |              |              |    |

| Arunkumar              |              |              | ✓  |              | $\checkmark$ | ✓            |   |              |              |              |    | $\checkmark$ |              |    |

| Kuppusamy              |              |              |    |              |              |              |   |              |              |              |    |              |              |    |

# CONFLICT OF INTEREST STATEMENT

Authors state no conflict of interest

## DATA AVAILABILITY

Data availability is not applicable to this paper as no new data were created or analyzed in this study

#### REFERENCES

- [1] N. V. Kumar and D. F. V. Lloyd, "Review on low power alu design using various techniques," *International Journal of Communication Networks and Information Security*, vol. 15, no. 04, pp. 352–359, 2023, doi: 10.36893/ijcnis.2023.V15I4.7147.

- [2] Y. Wu et al., "A survey on approximate multiplier designs for energy efficiency: from algorithms to circuits," ACM Transactions on Design Automation of Electronic Systems, vol. 29, no. 1, pp. 1–37, Jan. 2024, doi: 10.1145/3610291.

- [3] B. V. V. Satyanarayana and M. D. Prakash, "Device and circuit level design, characterization and implementation of low power 7T SRAM cell using heterojunction tunneling transistors with oxide overlap," *Microprocessors and Microsystems*, vol. 77, p. 103164, Sep. 2020, doi: 10.1016/j.micpro.2020.103164.

- [4] M. Bansal and J. Singh, "Qualitative analysis of 2-bit CMOS magnitude comparator and GDI magnitude comparator using FinFET technology (18 nm)," in 2020 International Conference on Smart Electronics and Communication (ICOSEC), Sep. 2020, pp. 1323–1327, doi: 10.1109/ICOSEC49089.2020.9215251.

- [5] D. Tripathi and S. Wairya, "A cost-efficient magnitude comparator and error detection circuits for nano-communication," in *Lecture Notes in Networks and Systems*, vol. 204 LNNS, 2021, pp. 239–254.

- [6] K. N. Vijeyakumar, P. T. N. K. Joel, S. H. S. Jatana, N. Saravanakumar, and S. Kalaiselvi, "Area efficient parallel median filter using approximate comparator and faithful adder," *IET Circuits, Devices & Systems*, vol. 14, no. 8, pp. 1318–1331, Nov. 2020, doi: 10.1049/iet-cds.2020.0059.

- [7] M. R. Machupalli, K. Challa, M. K. Bathula, G. R. Kumar, and R. Posupo, "Evaluation and performance analysis of magnitude comparator for high-speed VLSI applications," in *Smart Innovation, Systems and Technologies*, vol. 289, 2022, pp. 335–343.

- [8] H. Zhuang, C. Tong, X. Peng, and H. Tang, "Low-power, low-noise edge-race comparator for SAR ADCs," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 28, no. 12, pp. 2699–2707, Dec. 2020, doi: 10.1109/TVLSI.2020.3021680.

- [9] M. Jang et al., "Design techniques for energy-efficient analog-to-digital converters," IEEE Open Journal of the Solid-State Circuits Society, vol. 3, pp. 145–161, 2023, doi: 10.1109/OJSSCS.2023.3311418.

- [10] B. Jeevan and K. Sivani, "Design of 64-bit signed magnitude comparator using FPGA for IoT applications," in 2022 International Conference on Advances in Computing, Communication and Applied Informatics (ACCAI), Jan. 2022, pp. 1–5, doi: 10.1109/ACCAI53970.2022.9752617.

- [11] M. Sanadhya and D. K. Sharma, "Adiabatic logic based energy efficient architecture of 1-bit magnitude comparator for IoT applications," *Journal of Internet Technology*, vol. 23, no. 7, pp. 1643–1649, 2022, doi: 10.53106/160792642022122307018.

- [12] D. C. Arunabala, P. V. S. Ranjitha, B. L. G. Sravya, B. Navyasree, and A. Mounika, "Design of diversified low power and high-speed comparators using 45 nm Cmos technology," *International Journal of Innovative Technology and Exploring Engineering*, vol. 11, no. 5, pp. 27–31, Apr. 2022, doi: 10.35940/ijitee.E9849.0411522.

- [13] S. Lubaba, K. M. Faisal, M. S. Islam, and M. Hasan, "Design of a two-bit magnitude comparator based on pass transistor, transmission gate and conventional static CMOS logic," in 2020 11th International Conference on Computing, Communication and Networking Technologies, ICCCNT 2020, Jul. 2020, pp. 1–5, doi: 10.1109/ICCCNT49239.2020.9225501.

- [14] P. O. Beaulieu, F. Nabki, and M. Boukadoum, "8-bit partial magnitude comparator for spike generation in the leaky integrate-and-fire neuron model using gate-diffusion-input logic gates," in *ICECS 2022 29th IEEE International Conference on Electronics, Circuits and Systems, Proceedings*, Oct. 2022, pp. 1–4, doi: 10.1109/ICECS202256217.2022.9970788.

- [15] M. Rafiee, N. Shiri, A. Sadeghi, A. Darabi, and E. Abiri, "Low-power and fast-swing-restoration GDI-based magnitude comparator for digital images processing," *Circuits, Systems, and Signal Processing*, vol. 41, no. 9, pp. 4848–4885, Sep. 2022, doi: 10.1007/s00034-022-01997-6.

- [16] D. N. Mukherjee, S. Panda, and B. Maji, "Design and optimization of reversible logic based magnitude comparator using gate diffusion input technique," *IETE Journal of Research*, vol. 69, no. 6, pp. 3625–3637, Aug. 2023, doi: 10.1080/03772063.2021.1912658.

- [17] R. Sindhuja, E. J. Alex, and K. N. Reddy, "Efficient two-bit magnitude comparator with hybrid logic approach," in *Lecture Notes in Networks and Systems*, vol. 1200, 2025, pp. 629–644.

- [18] N. Shiri, A. Sadeghi, M. Rafiee, and M. Bigonah, "SR-GDI CNTFET-based magnitude comparator for new generation of programmable integrated circuits," *International Journal of Circuit Theory and Applications*, vol. 50, no. 5, pp. 1511–1536, May 2022, doi: 10.1002/cta.3251.

- [19] H. Chen, K. Abnoosian, and A. S. Mohammed, "An efficient design of a three-layer magnitude comparator for nano-scale IoT applications based on QCA technology," *Journal of Nanoelectronics and Optoelectronics*, vol. 19, no. 5, pp. 459–464, May 2024, doi: 10.1166/jno.2024.3587.

- [20] R. Singh and M. Gupta, "Comparative analysis of power consumption in 4-Bit magnitude comparators implemented in 130nm and 90nm CMOS technologies," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 30, no. 6, pp. 234–245, 2019.

- [21] H. S. Bindra, C. E. Lokin, D. Schinkel, A.-J. Annema, and B. Nauta, "A 1.2-V dynamic bias latch-type comparator in 65-nm CMOS with 0.4-mV input noise," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 7, pp. 1902–1912, Jul. 2018, doi: 10.1109/JSSC.2018.2820147.

- [22] S. Chevella, D. O'Hare, and I. O'Connell, "A low-power 1-V supply dynamic comparator," IEEE Solid-State Circuits Letters, vol. 3, pp. 154–157, 2020, doi: 10.1109/LSSC.2020.3009437.

- [23] N. Kandasamy, V. Dhare, and N. Telagam, "Novel optimized ultra-dense 1-bit magnitude comparator design in quantum-dot cellular automata technology based on MV32 gate," *Journal of Supercomputing*, vol. 78, no. 17, pp. 18666–18690, Nov. 2022, doi: 10.1007/s11227-022-04604-2.

- [24] V. K. Sharma, "Optimal design for digital comparator using QCA nanotechnology with energy estimation," *International Journal of Numerical Modelling: Electronic Networks, Devices and Fields*, vol. 34, no. 2, Mar. 2021, doi: 10.1002/jnm.2822.

- [25] M. Darbandi, S. Seyedi, and H. M. R. Al-Khafaji, "An efficient new design of nano-scale comparator circuits using quantum-dot technology," *Heliyon*, vol. 10, no. 18, p. e36933, Sep. 2024, doi: 10.1016/j.heliyon.2024.e36933.

- [26] F. Ntouskas, C. Efstathiou, and K. Pekmestzi, "Efficient design of magnitude and 2's complement comparators," *Integration*, vol. 71, pp. 164–169, Mar. 2020, doi: 10.1016/j.vlsi.2019.11.015.

- [27] C. Estathiou and P. Kitsos, "Efficient majority logic magnitude comparator design," *Microprocessors and Microsystems*, vol. 82, p. 103832, Apr. 2021, doi: 10.1016/j.micpro.2021.103832.

20 ISSN: 2252-8776

### **BIOGRAPHIES OF AUTHORS**

**Dr.** Anitha Juliette Albert professor in Electronics and Communication Engineering, has 18 years of teaching and 3 years of industry experience. With a Ph.D. from Anna University for her work on asynchronous VLSI architectures, her research focuses on low-power VLSI design, signal processing, and open-source VLSI tools. She can be contacted at email: anithajuliette.a@licet.ac.in.

Ashlin Leon A. S. Description is currently pursuing his bachelor of engineering (B.E.) in Electronics and Communication Engineering (ECE) at Loyola-ICAM College of Engineering and Technology (LICET), Chennai. His main areas of interest include signals and systems, VLSI and communication technologies used in real-world applications. He is passionate about learning new technologies and contributing to innovative projects. He can be contacted at email: ashlinleon.25ec@licet.ac.in.

Sinthia Panneer Selvam is working in the Department of Biomedical Engineering, Saveetha Engineering College. She has completed her B.Tech. in biomedical engineering in the year 2008, completed her M.Tech. in embedded systems in the year 2011. She pursued her research in the field of medical image processing and completed her doctorate in the year 2017. She has presented research articles in about 15 National and International Conferences and has also published 23 International Journals. She is currently continuing her research work in the area early detection of cancer. She can be contacted at email: sinthiapanneerselvam@gmail.com.

Dr. Sripriya Thiagarajan associate professor in the Department of Electronics and Communication Engineering has 19.7 years of experience in teaching. Her areas of interest include MEMS, digital signal processing, and IoT. She completed her B.E in the year 2002(University gold medallist and college first), M.E. - Applied Electronics in 2007 and Ph.D. in the year July 2019. She has published papers in International Journals and Conferences. She holds more than 3.2 lakhs Seminar funding from ICSSR, NHRC, BRNS, and CSIR. She also holds 6 published idea patents and 1 grant patent. She is currently working in Jeppiaar Institute of Technology (An Autonomous Institution), Kunnam Sunguvarchatram, Sriperumbudur, Tamil Nadu, India. She can be contacted at email: priyasri81@gmail.com.

Arunkumar Kuppusamy © © completed his bachelor's degree in Electronics and Communication Engineering from Anna University, Chennai, Tamilnadu, India, in the year 2011 and master's degree in applied electronics from Anna University, Chennai, Tamil Nadu, India, in the year 2013. He is currently working as assistant professor in the Department of Electronics and Communication Engineering, Saveetha Engineering College, Chennai, Tamilnadu, India and pursuing his doctoral degree in part-time at Anna University, Chennai, Tamil Nadu, India. He has a teaching experience of 11 years (2013-2024). He has published research papers in International Journals and Conferences. His areas of interest include VLSI design, MEMS, and image processing. He can be contacted at email: arunkumar@saveetha.ac.in.